下表列出了 5V CMOS 的輸入電壓閾值、 3.3VLVTTL 和 LVCMOS 的輸出驅動電壓。

從上表看出, 5V CMOS 輸入的高、低輸入電壓閾值均比 3.3V 輸出的閾值高約一伏。因此,即使來自 3.3V 系統的輸出能夠被補償,留給噪聲或元件容差的余地也很小或者沒有。我們需要的是能夠補償輸出并加大高低輸出電壓差的電路。

輸出電壓規范確定后,就已經假定:高輸出驅動的是輸出和地之間的負載,而低輸出驅動的是 3.3V和輸出之間的負載。如果高電壓閾值的負載實際上是在輸出和 3.3V 之間的話,那么輸出電壓實際上要高得多,因為拉高輸出的機制是負載電阻,而不是輸出三極管。

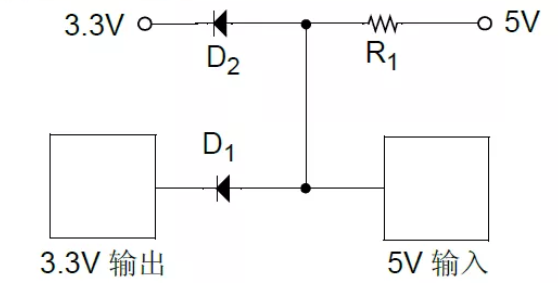

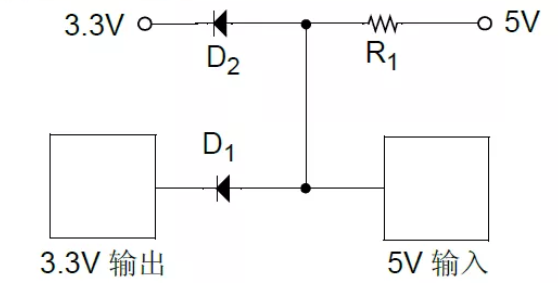

如果我們設計一個二極管補償電路 (見圖 7-1),二極管 D1 的正向電壓 (典型值 0.7V)將會使輸出低電壓上升,在 5V CMOS 輸入得到 1.1V 至1.2V 的低電壓。它安全地處于 5V CMOS 輸入的低輸入電壓閾值之下。輸出高電壓由上拉電阻和連至3.3V 電源的二極管 D2 確定。這使得輸出高電壓大約比 3.3V 電源高 0.7V,也就是 4.0 到 4.1V,很安全地在 5V CMOS 輸入閾值 (3.5V)之上。

注: 為了使電路工作正常,上拉電阻必須顯著小于 5V CMOS 輸入的輸入電阻,從而避免由于輸入端電阻分壓器效應而導致的輸出電壓下降。上拉電阻還必須足夠大,從而確保加載在 3.3V 輸出上的電流在器件規范之內。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹